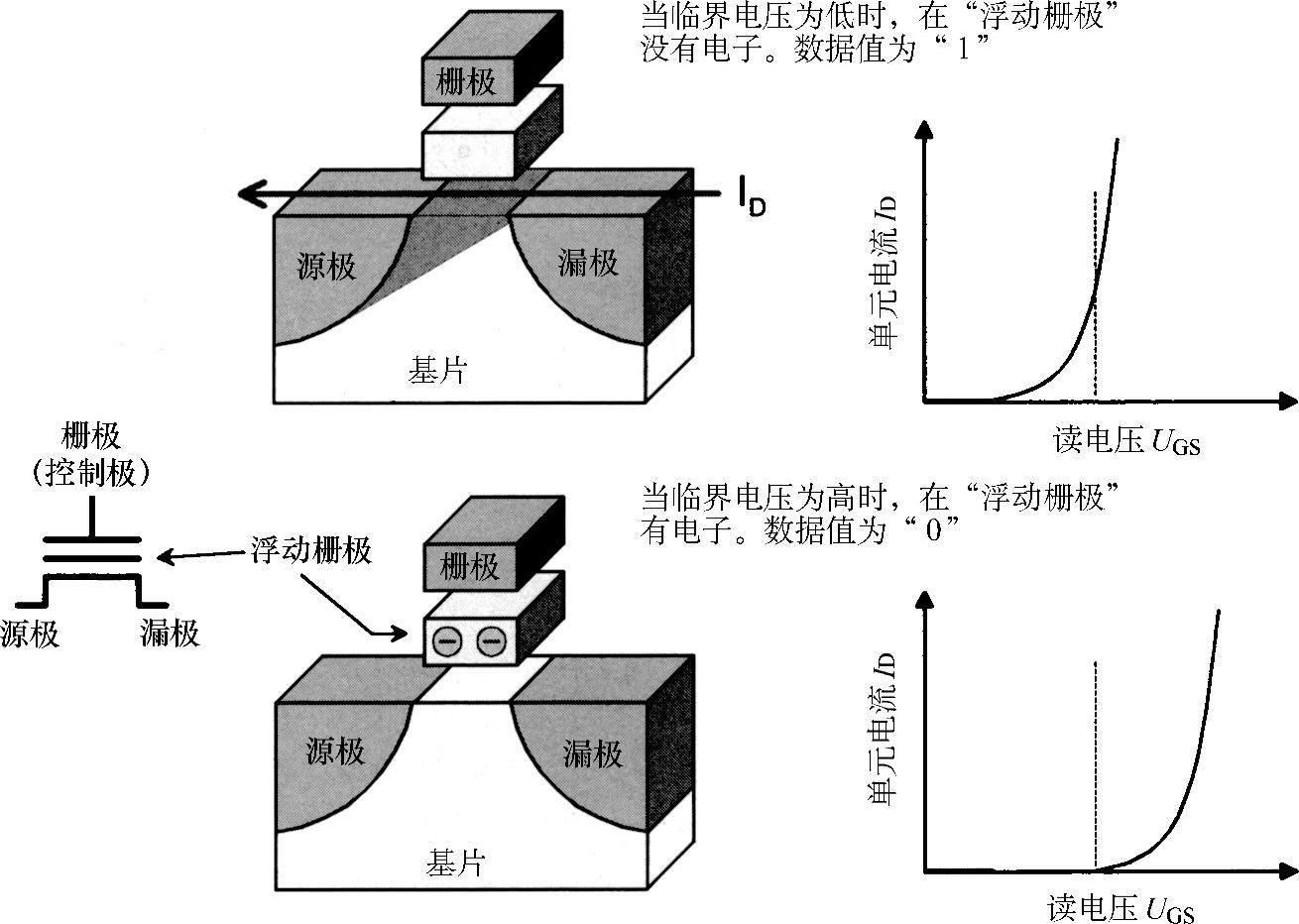

Flash存储器使用的是带浮动栅极的MOS场效应管。电子进入到栅极和源极-漏极沟道之间的绝缘层中,即形成浮动栅极。Flash存储器的最小单位是存储单元,这种最小的存储单元一般由单个晶体管组成(图8-4-1)。

图8-4-1 Flash存储单元结构

由于电子的进入,晶体管的临界电压(或称门槛电压)发生偏移,即为了导通晶体管必须在其栅极设置最小电压。在读出存储器内容时,必须在栅极设置正向电压(读电压),这个电压比没有导通时的栅极电压要大。在晶体管电路中称为逻辑1,即在浮动栅极没有电子,所以在读数据时,晶体管是导通的。在逻辑0时,在编程过程中向栅极充电,因此临界电压一般要升高,所以在编程过程中晶体管是不导通的。在删除和编程过程中,浮动栅极的放电和充电是借助于雪崩和量子效应实现的。这和福勒隧道效应是一样的。这种效应要求很完整的半导体结构,否则会损害绝缘体。因此删除和编程过程不能任意地经常进行,一般不超过100000次,否则存储单元的可靠性就会受到影响。和所有的半导体一样,如果经常在高温下运行的话,可靠性就会按近似指数函数下降。(www.zuozong.com)

在编程过程中,浮动栅极的充电和放电需要很高的电压,这种电压是借助于Flash-ROM内部的充电泵,根据标准电压产生的,并通过附加的电路结构设置到存储单元上。因此为了限制必要的费用,不按单独的存储单元删除,而是按整个、相对较大的存储块即按扇区进行删除。如一般是在总的2MB大小的存储器中,按64KB的数据块进行的。删除和编程过程是比较慢的。在读存储器数据时只需要10ns,而在删除存储器块时则需几百毫秒到几秒的时间。每个字节的编程持续时间少于10μs。

删除和编程过程是通过标准的数据和地址总线,用普通的写和读控制信号引导进行的。为了避免随机的删除,某些控制命令顺序要遵循规定的时间流程。因为程序的算法与制造商和类型有关,所以在Flash-Lader的内部,这种算法与被定义的接口和Flash驱动组件一起封装。

在删除和编程过程,许多组件不仅涉及存储块而且还涉及不可再访问的大部分甚至总的组件,所以来自于其他存储器组件的程序算法必须被执行。因此程序算法经常被复制到控制器的RAM并从这里开始被执行。为了保证编程过程不被未经许可或由于随机的控制器软件的错误功能所执行,人们要通过一定的措施来确认上述算法,此外也可采用通过诊断接口从外部向控制器内部装载关于Flash过程的算法。对于较新的组件,经常称存储器块中的一个为启动块(Boot Block),在第一次持续编程之后,要对删除和新的程序进行保护。这些块特别适合控制器的启动软件,即程序在设备接通之后执行,基本程序包含对于计算核心的初始化、存储器的测试,有时还有关于Flash编程的核心软件。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。